目前在车辆GPS导航系统中,主要是直接利用无差分、无SA误差的GPS定位数据来实现车辆在地图上的定位。考虑到定位信号存在一定的误差,5%概率下误差会超过15 m,同时城市中建筑物、桥梁以及树木等还对GPS信号形成遮挡,甚至会导致信号失效,从而进一步影响定位精度。而车在行进过程中进行导航时,尤其是在路口以及立交桥等特殊地点的导航时,系统往往需要更为精确的定位。为此,本设计充分利用了FPGA强大的逻辑控制功能和NiosⅡ处理器的多可配置标准外设接口功能,结合GPS和GSM功能模块,设计了一款双重定位系统。通常情况下用GPS进行定位,在特殊情况下可以开通GSM网络定位功能实现双定位,再通过GSM网络将定位信息、时间和终端特殊信息传送到监控中心,或者接收监控中心传来的信息,完成定位和监控等功能。

1 NiosⅡ软核嵌入式处理器

NiosⅡ处理器是Altera公司的第二代用户可配置的通用32位RISC软核微处理器,是Altera公司特有的基于通用FPGA架构的软CPU内核。N-iosⅡ系列支持使用专用指令。专用指令是用户增加的硬件模块,它增加了算术逻辑单元(ALU)。用户能为系统中使用的每个NiosⅡ处理器创建多达256个专用指令,这使得设计者能够细致地调整系统硬件以满足性能目标。专用指令逻辑和本身NiosⅡ指令相同,能够从多达两个源寄存器取值,可选择将结果写回目标寄存器。同时,NiosⅡ系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。在FPGA中使用软核处理器比硬核的优势在于,硬核实现没有灵活性,通常无法使用最新的技术。随着系统日益先进,基于标准处理器的方案会被淘汰,而基于NiosⅡ处理器的方案是基于HDL源码构建的,能够修改以满足新的系统需求,避免了被淘汰的命运。将处理器实现为HDL的IP核,开发者能够完全定制CPU和外设,获得恰好满足需求的处理器。

2系统的硬件设计与实现

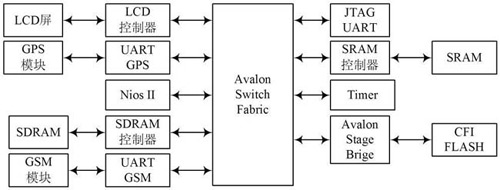

定位终端系统的硬件由一块FPGA芯片和GPS模块,GSM模块,外部存储SDRAM,FLASH,SRAM,LCD及控制模块等组成,其结构框图如图所示。FPGA芯片主要实现NiosⅡ软核处理器、片上存储器和各种接口驱动等功能,其包括NiosⅡ系统和外设两部分。NiosⅡ系统包括NiosⅡ处理器、存储器、定时器、串行接口、并行接口和连接各个组件的Avalon交换结构总线。其中GPS_UART和GSM_UART分别实现与GPS和GSM模块的串行通信,LCD控制器实现与人机交互模块的连接。

车载导航系统的硬件结构框图

2.1 GPS和GSM模块

对于GPS模块,采用Zarlink公司的GP2015,它的主要任务是对接收到的GPS信号进行外差式下变频,内部包括一个片内频率合成器、三级混频器、自动增益控制电路及量化器。在其内部使用锁相环频率合成器合成本地参考信号,然后和接收信号进行混频。在该系统设计中,射频前端GP2015需要两个外部时钟,一个是10 MHz的基准频率,另一个是其内部A/D的采样时钟,频率为5.714 MHz;在GPS接收机的设计中,射频前端与基带处理模块的时钟相位保持一致或相位误差比较小时,有助于提高接收机的定位精度。考虑到这一点,在本设计中FPGA和射频前端共用一个时钟源,给FPGA提供一个40 MHz的基准频率,FPGA经过内部的锁相环提供10 MHz和5.714 MHz的时钟信号给射频前端,保证了前端和基带处理时钟的同源。在GP2015内部还集成了一个两位A/D转换器,模拟中频输入为4.309 MHz,输出两位的数字中频信号,频率为1.405 MHz。GSM模块采用Siemens公司的TC35,该型号的GSM模块工作在EGSM 900 MHz和GSM1 800 MHz频率波段,提供话音和数据传输的无线连接,使用40引脚的零插力连接器作为控制数据、话音信号和电源线的应用接口。其串口通信波特率在300 b/s~115 Kb/s之间可选,也可以在1 200 b/s~115 Kb/s之间的8种波特率间自动适配。

2.2创建QuartusⅡ工程

创建项目工程名为GPS,芯片选型为EP2C20F484C7,并创建一个原理图文件GPS.bdf。

2.3启动SoPC Builder并配置硬件系统

将生成的NiosⅡ标准型CPU应用到系统中,debug level位设为1,系统复位映射到FLASH中,地址为0X0;异常映射到SRAM中,地址为0X-20.然后添加自己定制的LCD控制模块LCD_interface.v到NiosⅡ系统中。选择RS 232串口作为系统与GPS接收模块的接口,在系统构架中添加UAWT组件,命名为GPS_UART,波特率设为9 600 b/s.并选择DMA数据传输控制项。在组件中选择valonCornponenst/others/Interval Timer,在弹出的对话框中配置Initial Period项为1 ms,数据位宽为32。SDRAM作为存储介质保存数据,data width设为16,address width中row为12,column为8。添加SRAM模块用来存储程序,memory sizes为4 MB,添加CFI-Flash模块,用来存储图像及系统配置信息,在SoPC Builder左侧的组件栏中选择Avalon Components/Flash Memory,双击组件,选择address width为22,data width为8;还需要添加EPCS Controller,具体方法是:选择SoPC Builder左侧组件栏中的Avalon Components/Memory/EPCS Serial Flash Controller,单击Finish,完成组件添加。

添加Flash Controller模块,用来控制FLASH工作。由于FLASH的数据总线是三态的,所以NiosⅡCPU在与FLASH进行连接时需要添加Ava-lon总线三态桥控制模块Tri_state_bridge,用来连接FLASH模块;添加自己定制的GPS控制模块。最后添加系统ID模块。配置完成后选择Sy-stem Generation标签,单击Generate按钮,启动系统生成。

2.4创建QuartusⅡ顶层模块并集成NiosⅡ硬件系统

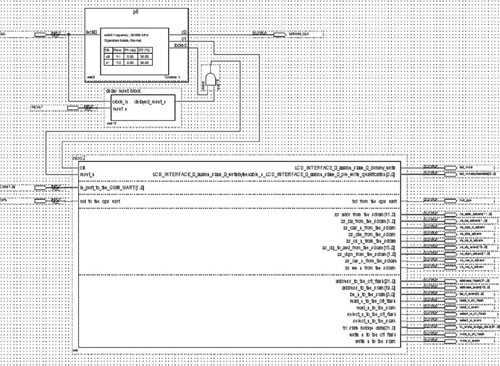

在GPS.bdf中添加生成的NiosⅡ系统,配置外围接口电路,生成完整的硬件系统构架。如图2所示。

硬件系统构架

选择Start Analysis&Synthesis开始分析和综合,完成后进行引脚分配,检查无误后执行Start Assembier,对输入设计进行汇编;将汇编好的编程配置文件GPS.sof通过JTAG方式下载到定位终端目标板上,即可完成硬件的所有综合设计。

3利用NiosⅡIDE进行系统软件设计

3.1软件总体构成

定位系统软件主要完成定位信息的采集和定位终端与监控中心之间的数据通信,主要由主程序、显示程序、GPS信息处理程序和GSM信息处理程序组成。主程序完成系统的初始化、自检、人机交互操作和定位信息的处理等功能。

3.2 GSM网络定位及通信

目前,中国移动和中国联通的移动通信网络既是语音通信网络,又是一个能提供丰富数据业务的网络,只要当地网络开通了位置服务功能,选用支持STK的SIM卡,即可通过STK命令得到位置信息。GSM网络通信主要以短消息的方式进行,包括短消息的接收和发送。在短消息的收发程序设计中运用AT命令来实现,其包括定位和监控信息的编码和解码、通信模式设定和联机测试、短消息的收发、收发数据的关键命令字的模式匹配。

3.3 GPS信号定位

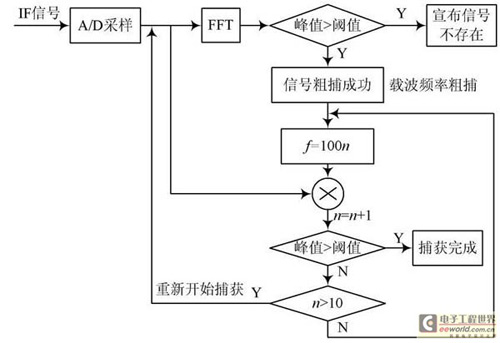

在进行信号稳定跟踪以前,首先需要实现信号的捕获来确定信号是否存在。通用接收机对载波信号的捕获通常采用一维的串行相关搜索。在本文所描述的高动态情况下,载波多普勒频偏最大为±14 kHz,若选择频率搜索步进为500 Hz,需要57次才能完成整个28 kHz带宽的搜索,显然非常耗费时间。而利用傅里叶变换将信号从时域变换到频域后,通过把原来的时域串行搜索变为频域并行搜索,进行1次并行搜索就能等同于传统方式下的57次串行搜索,大大节约了搜索时间。GPS定位流程如图3所示。

GPS定位流程